接合型電界効果トランジスタ

接合型電界効果トランジスタは、電圧制御される半導体ベースのトランジスタです。これらは 3 つの端子を持つ単方向トランジスタです。ドレイン、ソース、ゲート。 JFET には PN 接合はありませんが、半導体材料のチャネルで構成されています。

構造と分類

JFET には、多数電荷キャリアを流すための大きなチャネルがあります。このチャネルは基質として知られています。基板は、P 型または N 型の材料でできます。オーミックコンタクトとして知られる 2 つの外部コンタクトがチャネルの両端に配置されます。 JFET は、その構造における基板の半導体材料に基づいて分類されます。

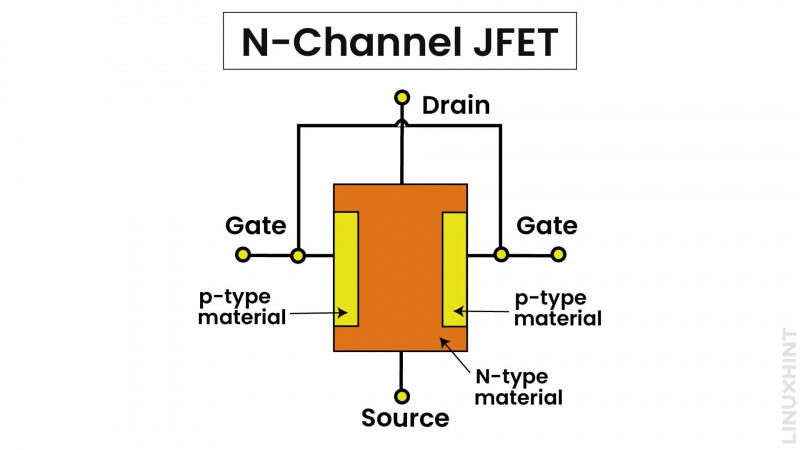

NチャンネルJFETトランジスタ

チャネルは N 型不純物材料で構成され、ゲートは P 型不純物材料で構成されます。 N 型材料とは、5 価の不純物がドープされており、大部分の電荷キャリアがチャネル内の自由電子であることを意味します。 N チャネル JFET の基本構造と記号表現を以下に示します。

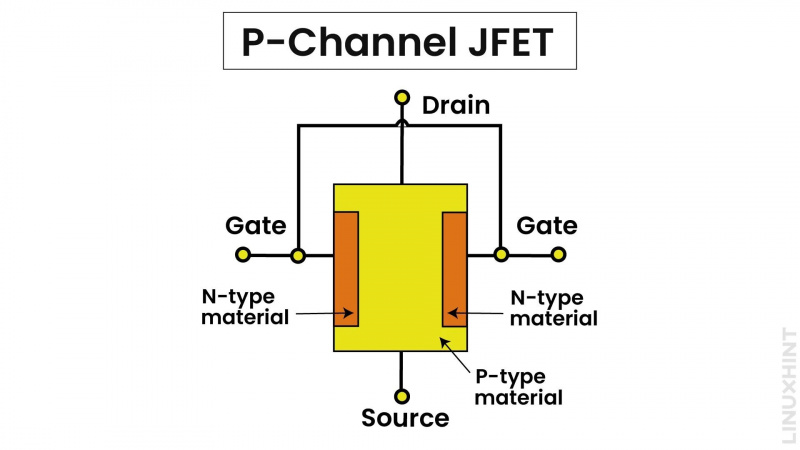

P チャネル JFET トランジスタ

チャネルは P 型不純物材料で構成され、ゲートは N 型不純物材料で構成されます。 P チャネルとは、チャネルに 3 価の不純物がドープされており、多数の電荷キャリアが正孔であることを意味します。 P チャネル JFET の基本構造と記号表現を以下に示します。

JFETの働き

JFET は、水道ホースのパイプに例えて説明されることがよくあります。パイプを通る水の流れは、JFET のチャネルを通る電子の流れに似ています。水道管の絞りによって水の流量が決まります。同様に、JFET の場合、ゲート端子間の電圧の印加によって、ソースからドレインへの電荷の移動のためのチャネルが狭くなるか広くなるかが決まります。

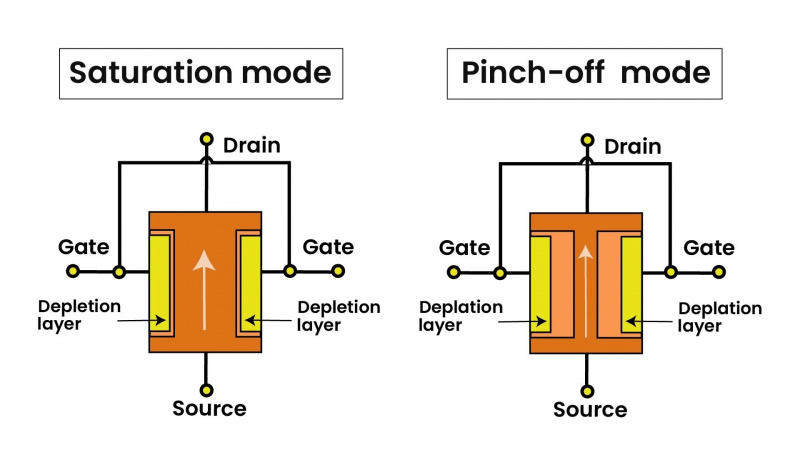

ゲートとソース間に逆バイアス電圧が印加されると、チャネルが狭くなり、空乏層が増加します。この動作モードはピンチオフ モードと呼ばれます。この種のチャネルの動作を以下に示します。

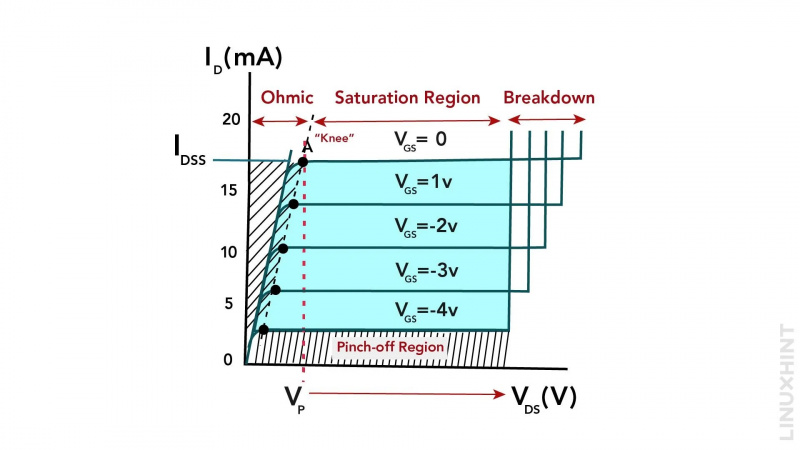

JFET特性曲線

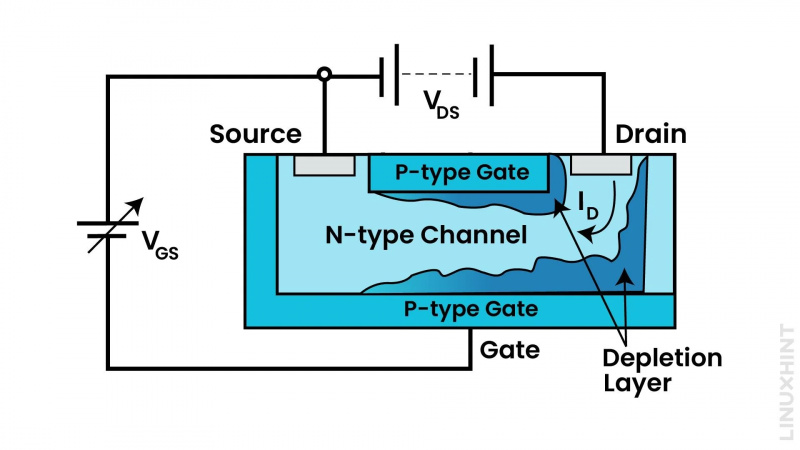

JFET は空乏モード デバイスです。つまり、空乏層の拡大または縮小で動作します。完全な動作モードを解析するために、次のバイアス配置が N チャネル JFET の両端に適用されます。

2 つの異なるバイアス電圧が JFET 端子に適用されます。上図に示すように、VDS はドレインとソースの間に印加され、VGS はゲートとソースの間に印加されます。

JFET は、以下で説明するように 4 つの異なる動作モードで動作します。

1: オームモード

オームモードは、端子間にバイアス電圧が印加されていない通常の状態です。したがって、オームモードでは VGS=0 になります。空乏層は非常に薄く、JFET は抵抗などのオーム素子のように動作します。

2: ピンチオフモード

カットオフモードでは、ゲートとソース間に十分なバイアス電圧が印加されます。印加された逆バイアス電圧は空乏領域を最大レベルまで引き伸ばすため、チャネルは電流の流れに抵抗する開いたスイッチのように動作します。

3: 飽和モード

ゲートおよびソースのバイアス電圧は、JFET のチャネルを流れる電流を制御します。電流はバイアス電圧の変化に応じて変化します。このモードでは、ドレインとソースのバイアス電圧の影響は無視できます。

4: ブレイクダウンモード

ドレインとソースのバイアス電圧は、JFET のチャネルの空乏層を破壊するレベルまで増加します。これにより、チャネル全体に最大の電流が流れます。

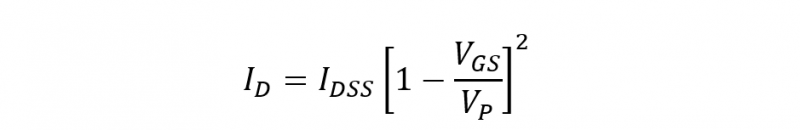

JFET パラメータの数学式

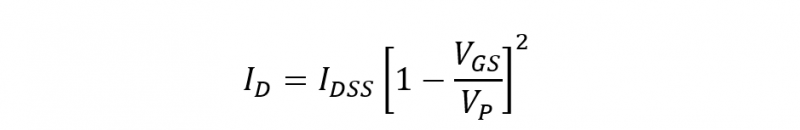

飽和モードでは、JFET は電圧によって電流が変化する導体モードに入ります。したがって、ドレイン電流を評価することができる。ドレイン電流を評価する式は次のようになります。

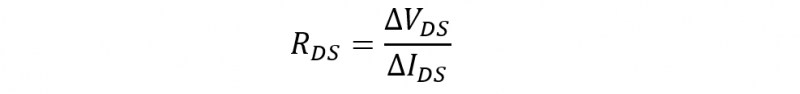

ゲート電圧を印加すると、チャネルが広くなったり狭くなったりします。ドレイン・ソース間電圧の印加に対するチャネルの抵抗は次のように表されます。

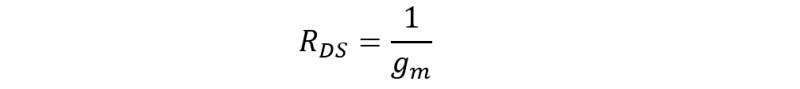

RDS は相互コンダクタンス ゲイン gm を通じて計算することもできます。

JFETの構成

JFET はさまざまな方法で入力電圧に接続できます。これらの構成は、共通ソース、共通ゲート、および共通ドレイン構成として知られています。

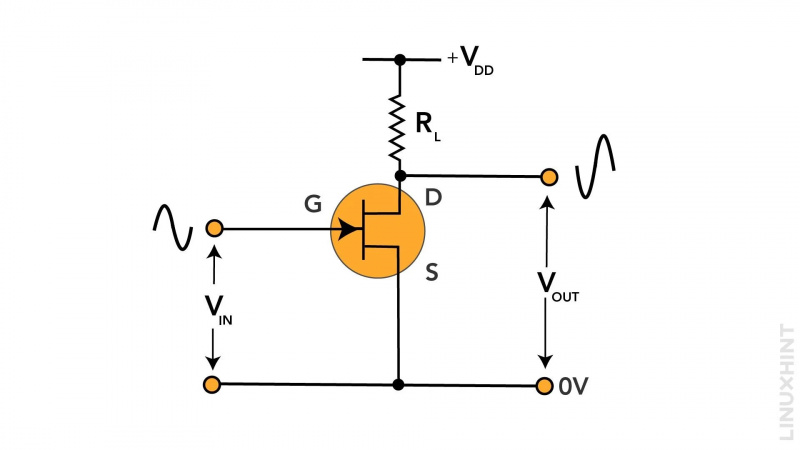

共通ソース構成

コモンソース構成では、JFET のソースは接地され、入力はゲート端子に接続され、出力はドレインから取られます。この構成により、高入力インピーダンスと電圧増幅機能が提供されます。このアンプ モード構成は、すべての JFET 構成の中で最も一般的です。得られる出力は入力に対して 180 度位相が異なります。

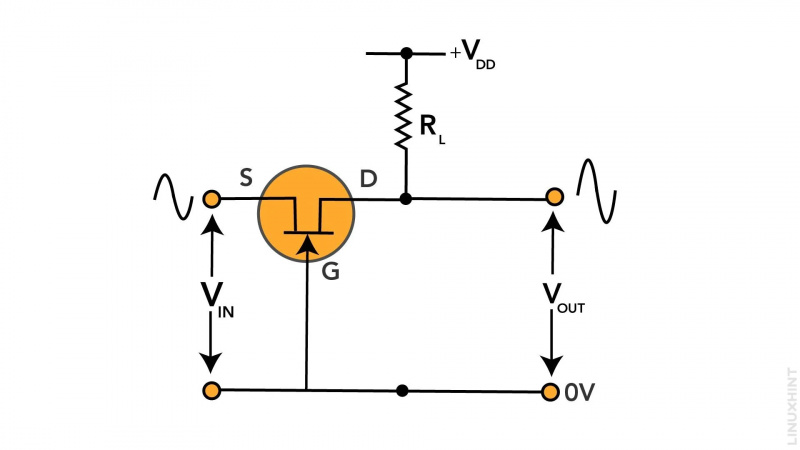

共通ゲート構成

コモンゲート構成では、ゲートは接地され、入力はソースに接続され、出力はドレインから取られます。ゲートがグランドに接続されているため、構成の入力インピーダンスは低くなりますが、出力のインピーダンスは高くなります。得られる出力は入力と同相です。

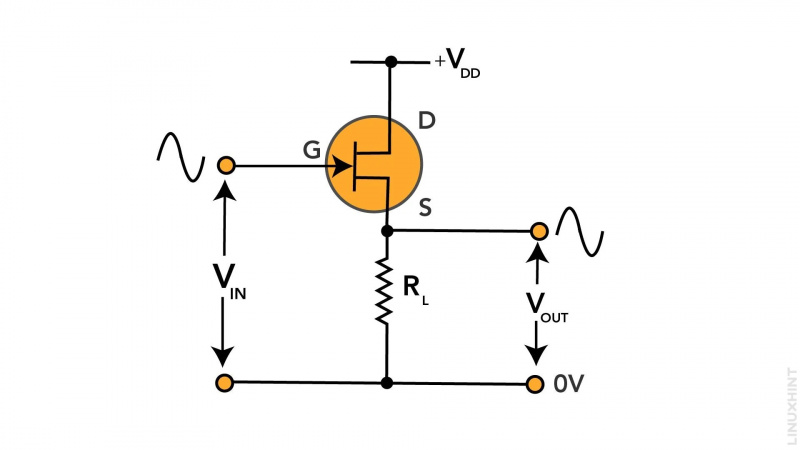

共通のドレイン構成

共通ドレインでは、入力はゲートに接続され、出力はソース端子に接続されます。この構成でも、共通ゲート構成と同様に、低い入力インピーダンスと高い出力インピーダンスが提供されますが、ここでの電圧ゲインはほぼ 1 です。

この構成は、入力がゲートに接続されている共通ソースにも適合しますが、共通ソース構成のゲインは 1 より小さくなります。

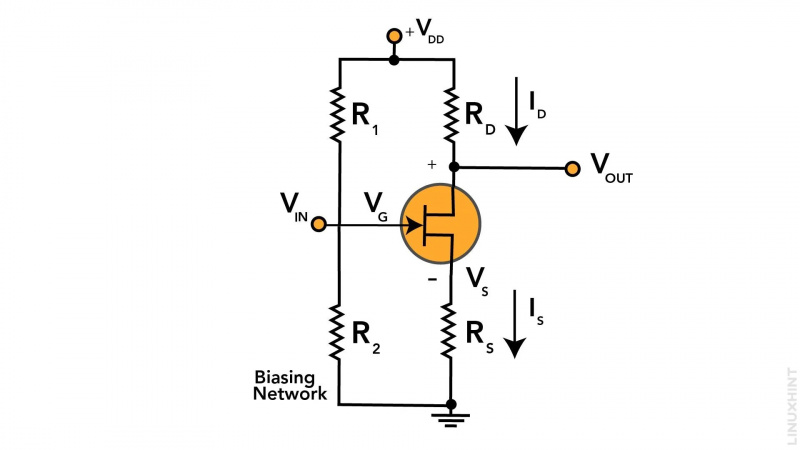

アプリケーション – JFET アンプ構成

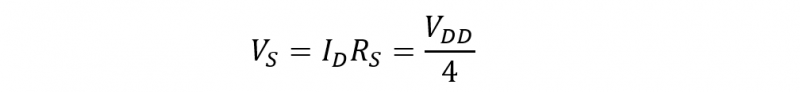

JFET は、ゲート端子が分圧器ネットワークに接続されている場合、クラス A アンプとして動作するようにできます。外部電圧はソース端子の両端に印加されます。以下の回路では、ソース端子は主に VDD の 4 分の 1 になるように構成されています。

したがって、電源電圧は次のように表すことができます。

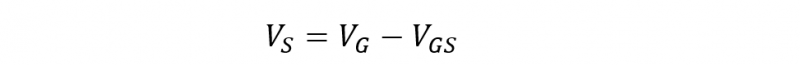

また、電源電圧は以下の式で計算できます。

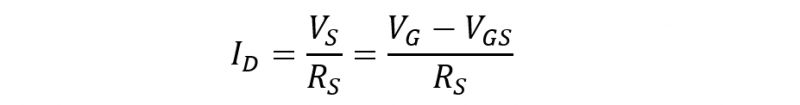

ドレイン電流は、上記の構成から次のように計算できます。

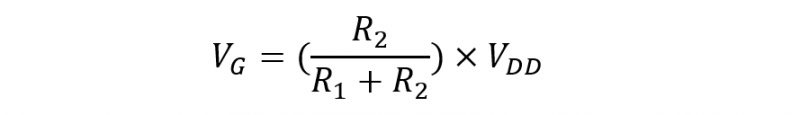

ゲート電圧は、以下に示すように、抵抗 R1 および R2 の値の関数として取得できます。

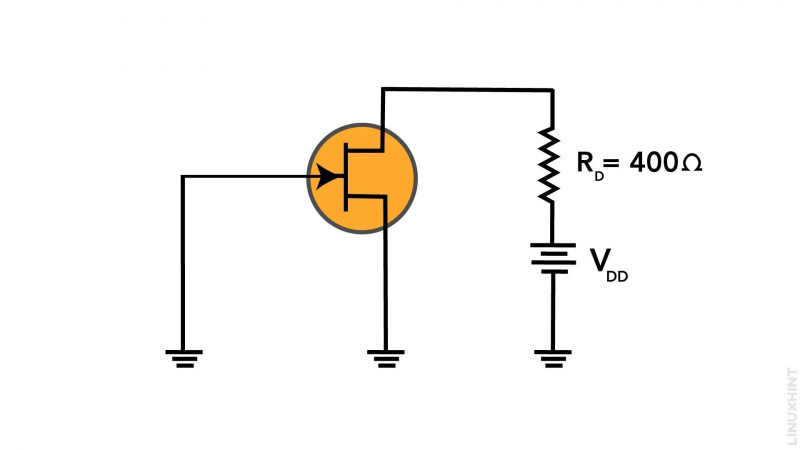

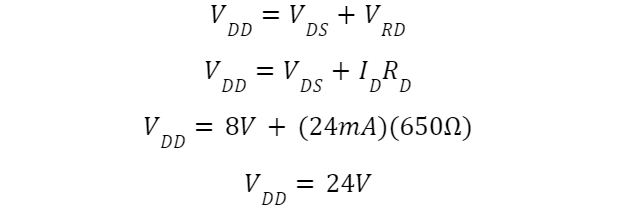

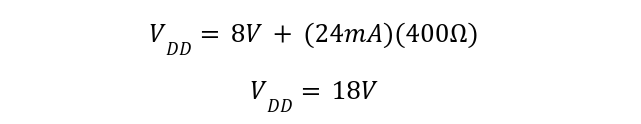

例 1: V の計算 DD

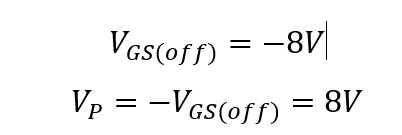

Vの場合 GS(オフ) =-8V、I DSS 以下の構成の JFET の場合 =24mA、V を計算します DD 図に示すように、R の場合 D =400。

以来

上記は、JFET が定電流領域で動作するための VDS の最小値であるため、次のようになります。

また、

ドレイン回路に KVL を適用すると、次のようになります。

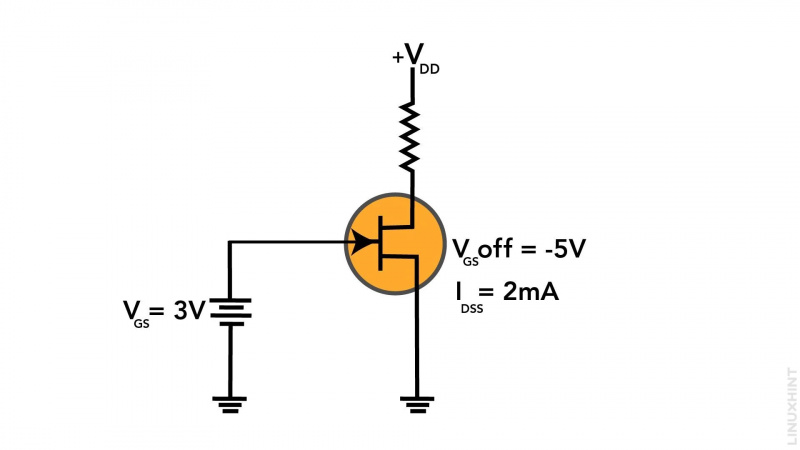

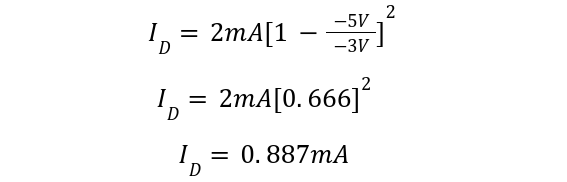

例 2: ドレイン電流の値を決定する

以下の JFET 構成で、VGS=3V、VGS(Off)=-5V、IDSS=2mA のときのドレイン電流の値を求めます。

ドレイン電流の式は次のとおりです。

結論

接合型電界効果トランジスタは、さまざまな動作モードで空乏領域の動作を扱う 3 端子半導体デバイスです。 PN 接合はありませんが、半導体材料のチャネルで構成されています。